Oplossingen van de opgaven van hoofdstuk 7

- Een computersysteem bestaat in het algemeen uit drie modules. CPU, MEMORY

en INPUT/OUTPUT. Deze modules zijn met elkaar verbonden via drie bussen:

adresbus, databus en controlebus.

- Een CPU met 20 adreslijnen kan 220 geheugenlocaties

adresseren. Als elke locatie 1 Byte is, is de adresseercapaciteit

220 bytes = 1 megabyte.

- Een exception is een bijzondere gebeurtenis, waarop de CPU op een speciale

voorgeschreven manier reageert. Voorbeelden van exceptions zijn: interrupts

(zowel hard- als software) en interne systeemproblemen (delen door nul, illegal

instructions, bus errors).

- Het verschil tussen de twee architecturen is het wel of niet scheiden van instructies en data. Bij de Harvard architectuur kennen de instructies een eigen geheugen en een eigen datapad naar de CPU.

- In onderstaande figuur is aangegeven hoe dit gerealiseerd moet

worden. Met de twee select-signalen S0 en S1 activeren we een van de

vier tristate buffer die dan zijn ingangssignaal (A, B, C of D) doorgeeft

naar de uitgang.

- De CPU kan 1 MByte adresseren. De databusbreedtes van RAM-module en CPU zijn

gelijk, dus we hoeven geen modules parallel te schakelen. We geven met

onderstaande schakeling elke module zijn eigen bereik in het totale adresbereik van

de CPU. De decoder kiest als gevolg van A18 en A19 een van de vier modules.

De overige adreslijnen van de CPU zijn met de overeenkomstige adreslijnen van

alle vier de RAM modules.

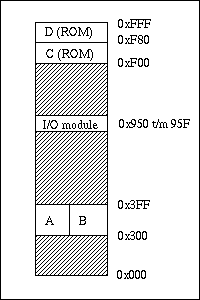

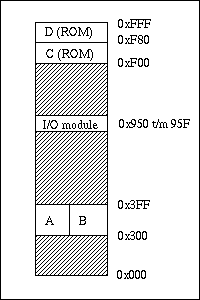

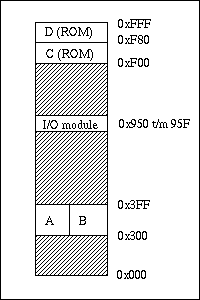

- De CPU van de figuur heeft 12 adreslijnen en een databus van 8 bits breed.

De totale adresseercapaciteit komt hiermee op: 212 Bytes = 4096 Bytes.

- A en B zijn RAM-modules omdat ze een Lees/Schrijf ingang bevatten en

bovendien over veel adreslijnen beschikken (dit in tegenstelling tot

I/O-poorten die meestal maar een paar adreslijnen hebben).

Met 8 adreslijnen en 4 bits per locatie is de opslagcapaciteit

28 x 4 bits = 1024 bits ofwel 128 Bytes.

- De ROM-modules hebben een opslagcapaciteit van 27 x 8 bits = 128 Bytes.

- De volgende figuur geeft een memory map met daarin de plaats van de aangesloten

modules. Let op: het is niet op schaal getekend. Module A en B staan parallel.

A bevat de even databits (D0, D2, D4 en D6), en B de oneven databits (D1, D3, D5 en D7).

Het gearceerde gedeelte is wel door de CPU te adresseren, maar hier bevinden zich geen

modules.

- Ox71 ziet er binair uit als 01110001. In module A worden de bits D0, D2, D4

en D6 opgeslagen. Dit is het bitgroepje 1101 (het laastste bit is D0 daarvoor D2

enzovoort). In module B worden de oneven bits opgeslagen. Deze vormen het

bitgroepje 0100.

- Aangezien de I/O poort over 4 adreslijnen beschikt kunnen er 24 = 16

registers geadresseerd worden (gegeven de voorwaarde van de opgave).